Comptadors

Els circuits seqüencials comptadors són circuits digitals capaços de passar per una seqüència ordenada d’estats en resposta a impulsos de rellotge. Cada estat representa un valor binari, i el circuit pot comptar cap endavant o cap enrere segons el disseny.

A diferència dels circuits combinacionals, l’estat actual d’un comptador depèn tant de les entrades com de l’estat anterior. Aquesta memòria s’implementa amb biestables, habitualment del tipus T, D o JK.

Els comptadors s’utilitzen en mesura de temps, generació de seqüències, divisió de freqüències i en blocs interns de rellotges digitals i processadors.

Els comptadors més comuns segueixen una seqüència binària: 0000, 0001, 0010, 0011, ..., i en arribar al valor màxim poden tornar a zero (comptador cíclic) o bé comptar enrere (bidireccional).

Comptador binari MOD

Un comptador MOD

S’utilitza per comptar, generar seqüències i dividir freqüències.

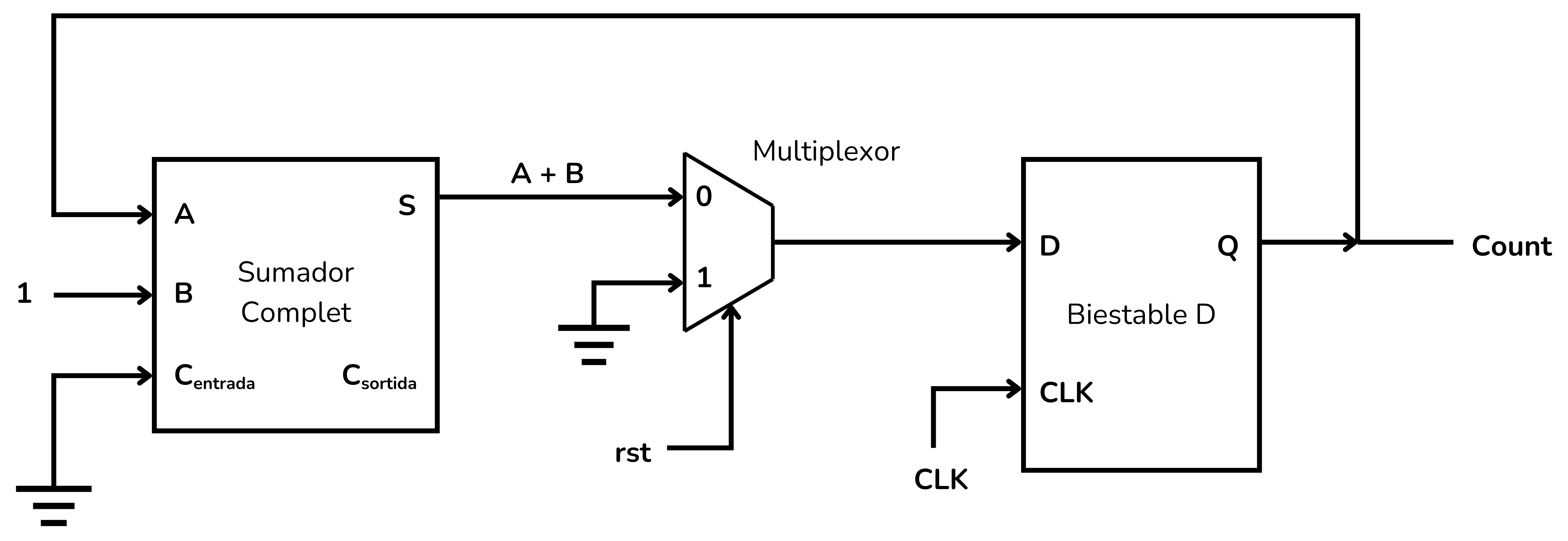

Comptador d’un sol bit MOD

El següent comptador té un sol bit, utilitza un sol biestable. És, per tant, un comptador MOD

Aquest comptador utilitza un biestable D, un sumador complet (full adder) i un multiplexor. El sumador suma sempre

El multiplexor serveix per afegir la possibilitat de reiniciar el comptador. El senyal selector actua doncs com un senyal de reinici (reset rst). Quan aquest senyal s’activa, el multiplexor connecta un valor constant

Funcionament

Per entendre com funciona aquest comptador, comencem amb el biestable en un estat

Estat inicial:

El biestable es troba en un estat

Aquest senyal, amb valor

El comptador és a zero (

Primer pols:

Quan s’aplica un pols de rellotge el valor de

El sumador hi suma el valor constant 1 i retornem al biestable el senyal

El bit de ròssec (carry) de sortida s'activa,

Ara l’entrada del biestable és

El comptador ha comptat fins a 1 (

Segon pols: El següent pols de rellotge actualitza còpia el valor

| Pols | |||

|---|---|---|---|

| 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 2 | 1 | 0 | 0 |

| 3 | 0 | 1 | 1 |

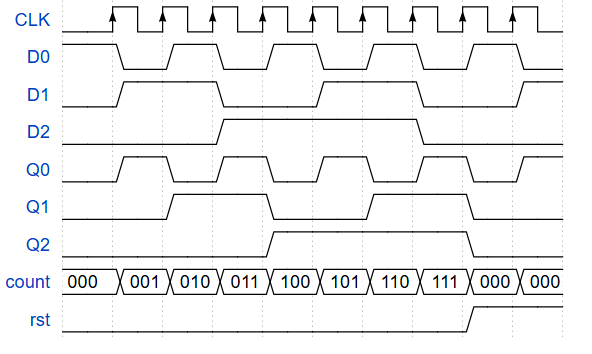

Podem visualitzar el funcionament d’aquest comptador amb el cronograma següent:

Sigui quin sigui l’estat del comptador, en el moment que activem el senyal de reinici (

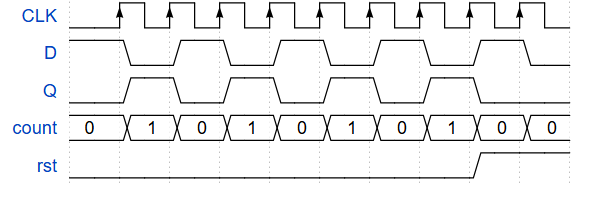

Comptador de 3 bits MOD

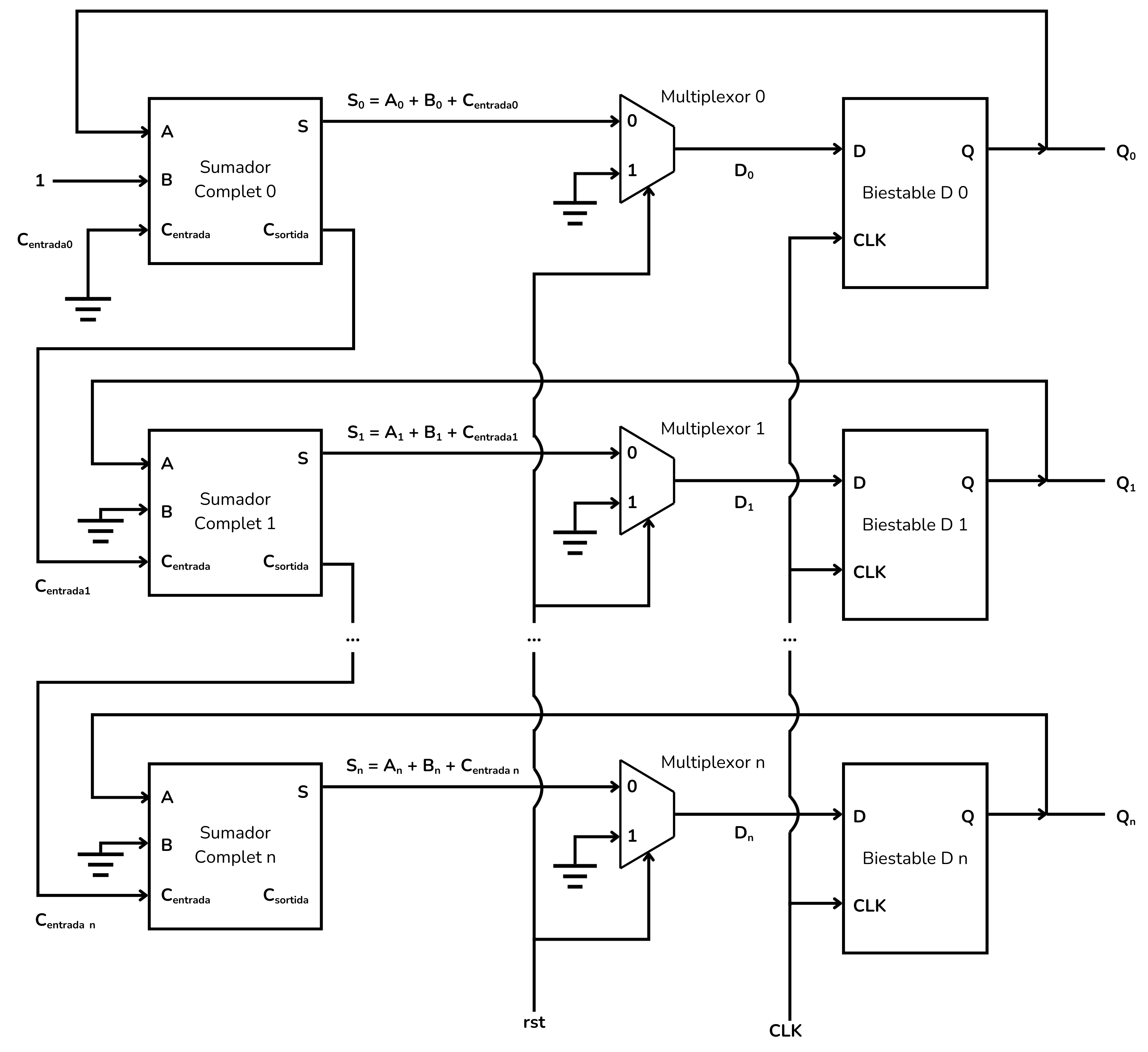

El següent comptador és de 3 bits, utilitza 3 biestables. És doncs un comptador MOD

Aquest comptador es compon de 3 biestables D, 3 sumadors complets i, per tal d’afegir la possibilitat de reiniciar el comptador, 3 multiplexors.

Dels biestables n’obtindrem una sortida de 3 bits

Aquest conjunt de 3 sumadors complets, és a dir, aquest sumador de 3 bits, afegirà contínuament la constant

El senyal de reinici (reset, o

Funcionament

Analitzem el funcionament d’aquest comptador, començant amb tots els biestables a zero. La taula, més endavant, recull el resultat d’aquesta anàlisi.

Estat inicial:

Els biestables estan en l’estat

El sumador 0 fa l'operació

El sumador 1 fa l'operació

El sumador 2 fa l'operació

No hi ha cap bit de ròssec (

Primer pols:

El pols de rellotge fa que els bits de

Per tant,

Segon pols:

El pols de rellotge fa que els bits de

Per tant,

Tercer pols:

El pols de rellotge fa que els bits de

Per tant,

Dos bits de ròssec de sortida estan activats,

Amb els següents polsos de rellotge, els biestables passen per totes les combinacions possibles, representant un nombre binari creixent fins a arribar al punt on tots els biestables són a l’estat 1. És a dir

Setè pols:

Hem arribat al valor màxim del comptador,

| Pols | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 000 |

| 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 1 | 001 |

| 2 | 0 | 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 010 |

| 3 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 1 | 011 |

| 4 | 1 | 0 | 1 | 0 | 0 | 0 | 1 | 0 | 0 | 100 |

| 5 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 1 | 101 |

| 6 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 110 |

| 7 | 0 | 0 | 0 | 1 | 1 | 1 | 1 | 1 | 1 | 111 |

| 8 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 0 | 000 |

Podem visualitzar el funcionament d’aquest comptador amb el cronograma següent:

Sigui quin sigui l’estat del comptador, en el moment que activem el senyal de reinici (rst), el multiplexor forçarà el comptador a retornar al seu estat inicial.

Comptador de n bits MOD

Per implementar un comptador de n bits cal encadenar n biestables, n sumadors i n multiplexors de la mateixa manera. Amb aquest comptador es pot comptar de 0 fins a

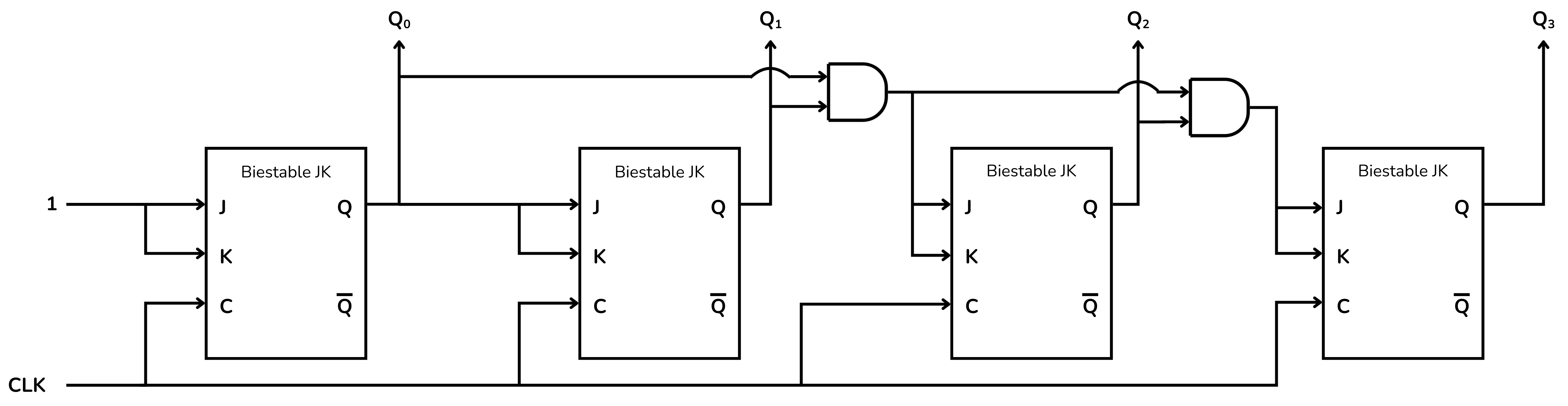

Comptador Binari Asíncron (Asynchronous Binary Counter o Ripple Counter):

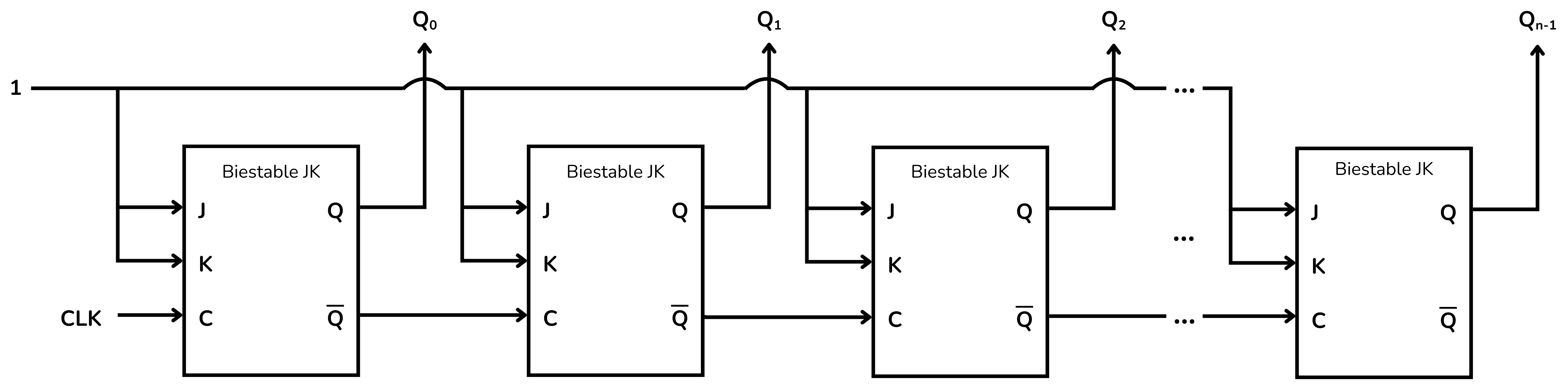

Un comptador binari asíncron (Asynchronous Binary Counter), o comptador en cascada (Ripple Counter), s’implementa amb una sèrie de biestables, normalment del tipus JK. El primer biestable representa el bit menys significatiu LSB, que és controlat pel rellotge, i cadascun dels següents pel senyal de sortida de l’anterior, de manera que aquests biestables canvien d’estat en cascada.

Els biestables JK estan connectats de manera que

i, per tant, l’estat de es commuta entre 0 i 1 quan entra un senyal de rellotge. Els biestables capten un senyal de rellotge només en el moment que aquest bit passa de 0 a 1. No es considerarà que entra senyal de rellotge mentres aquest es mantingui a 1, a 0 o commuti de 1 a 0.

La sortida

correspon al bit menys significatiu LSB la sortida correspon al bit més significatiu MSB. El senyal de rellotge extern s’aplica solament a l’entrada del primer biestable.

La sortida

de cada biestable es connecta a l’entrada de rellotge del següent biestable. Això significa que quan un biestable commuti Q de 1 a 0, Q’ passarà de 0 a 1, estimulant l’entrada de rellotge del biestable següent. I això produirà una commutació de l’estat al biestable següent.

Dit breument: un biestable commutarà d’estat només en el moment que el biestable anterior passa de 1 a 0.

Per entendre com funciona aquest comptador, comencem amb tots els biestables a ‘0’.

Primer pols:

El primer biestable

El segon biestable no detecta impuls a l’entrada de rellotge, no canvia d’estat i per tant

El tercer biestable i tots els següents continuen a 0.

Segon pols:

El primer biestable

El segon biestable detecta impuls a l’entrada de rellotge,

El tercer biestable i tots els següents continuen a 0.

Amb els següents polsos de rellotge. Les commutacions es van propagant de manera que els biestables passen per totes les combinacions possibles, representant un nombre binari creixent fins a arribar al punt on tots els biestables són a l’estat 1. En aquest punt, el següent pols de rellotge commuta el primer biestable de 1 a 0, el segon també, i així tots els biestables passen de 1 a 0 en cadena, tornant al punt de partida.

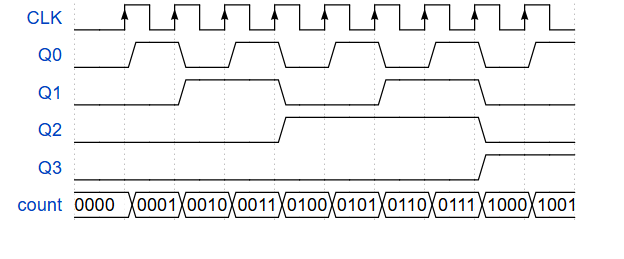

Aquesta taula mostra la seqüència dels diferents bits del comptador.

| Pols | |||||

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0000 |

| 1 | 0 | 0 | 0 | 1 | 1000 |

| 2 | 0 | 0 | 1 | 0 | 0100 |

| 3 | 0 | 0 | 1 | 1 | 1100 |

| 4 | 0 | 1 | 0 | 0 | 0010 |

| ··· | ··· | ··· | ··· | ··· | ··· |

| 14 | 1 | 1 | 1 | 0 | 0111 |

| 15 | 1 | 1 | 1 | 1 | 1111 |

| 16 | 0 | 0 | 0 | 0 | 0000 |

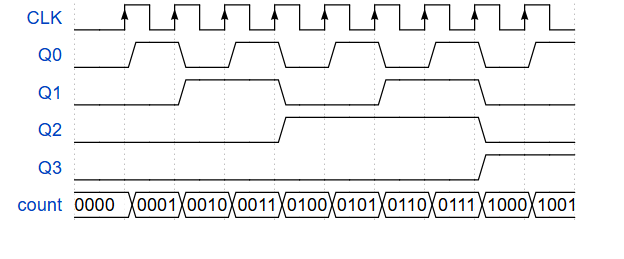

La figura següent mostra el cronograma d’aquest comptador.

Aquest tipus de comptadors acumulen retards de tots els biestables a l’hora de passar d’un estat al següent, per tant, no és adequat per a freqüències de rellotge altes.

Els comptadors són també divisors de freqüència. Cada bit s’activa a la meitat de la freqüència del bit anterior de manera natural. És doncs un dispositiu que divideix successivament per 2 la freqüència de rellotge.

Comptador Binari Síncron (Synchronous Binary Counter):

Un comptador binari síncron és molt similar als comptadors asíncrons, però en aquest cas tots els biestables reben el mateix senyal de rellotge i canvien d'estat simultàniament.

Utilitza biestables de tipus JK i té la següent estructura:

Al biestable 0 les entrades

La sortida del biestable 0 (

Les entrades

A partir del biestable 2, aquesta estructura es va repetint fins a completar el comptador.

Per entendre com funciona aquest comptador, comencem amb tots els biestables a ‘0’.

Estat inicial:

Tots els biestables estan a zero,

Primer pols:

El primer biestable

Segon pols:

Com que

Tercer pols:

Com que

Quart pols:

Per primera vegada, la porta AND s’activa al rebre

Amb els següents polsos de rellotge, els biestables passen per totes les combinacions possibles, representant un nombre binari creixent fins a arribar al punt on tots els biestables són a l’estat 1.

Tant la taula, com el cronograma amb la seqüència del comptador són idèntiques al comoptador anterior.

| Pols | |||||

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0000 |

| 1 | 0 | 0 | 0 | 1 | 1000 |

| 2 | 0 | 0 | 1 | 0 | 0100 |

| 3 | 0 | 0 | 1 | 1 | 1100 |

| 4 | 0 | 1 | 0 | 0 | 0010 |

| ··· | ··· | ··· | ··· | ··· | ··· |

| 14 | 1 | 1 | 1 | 0 | 0111 |

| 15 | 1 | 1 | 1 | 1 | 1111 |

| 16 | 0 | 0 | 0 | 0 | 0000 |

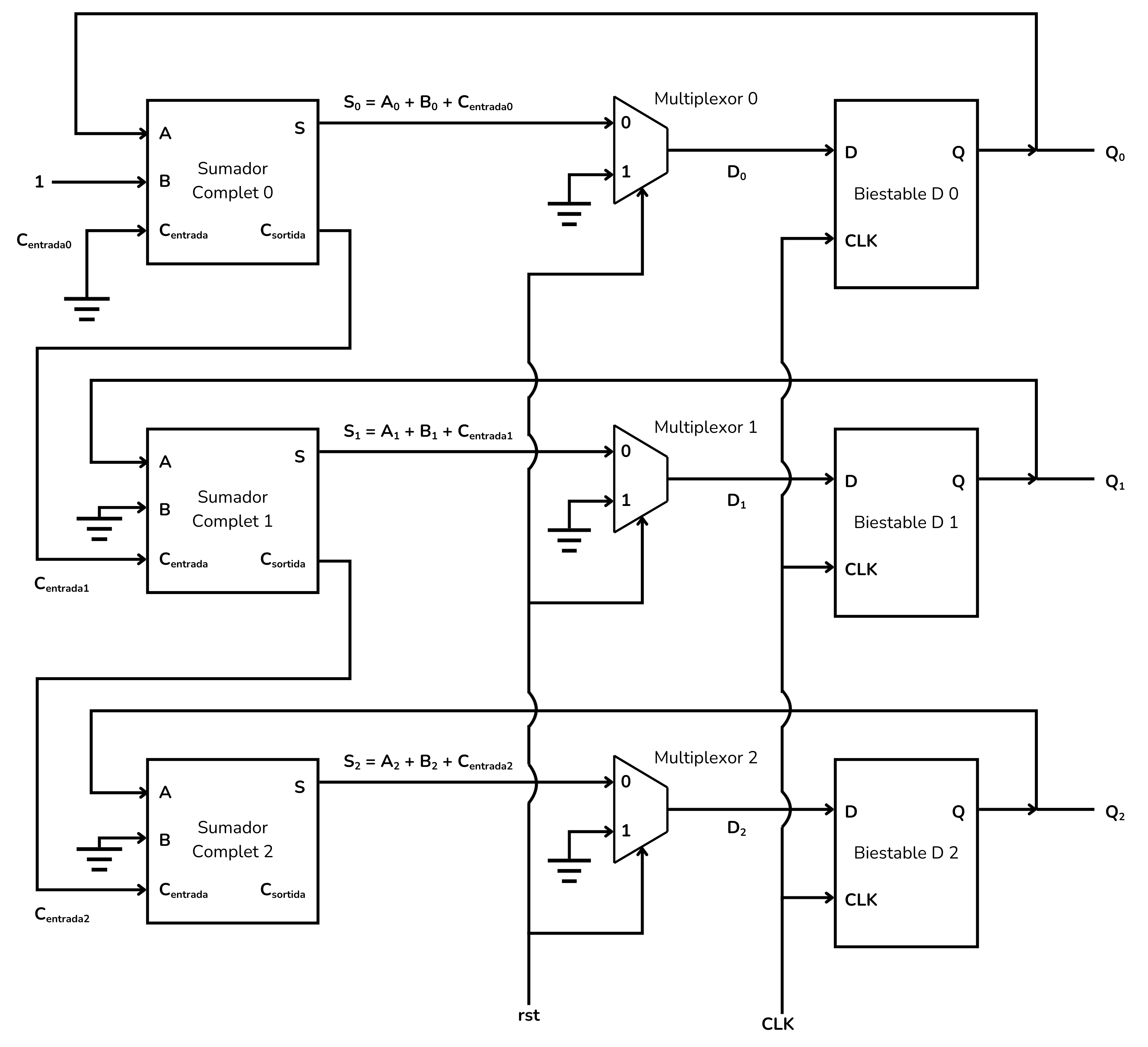

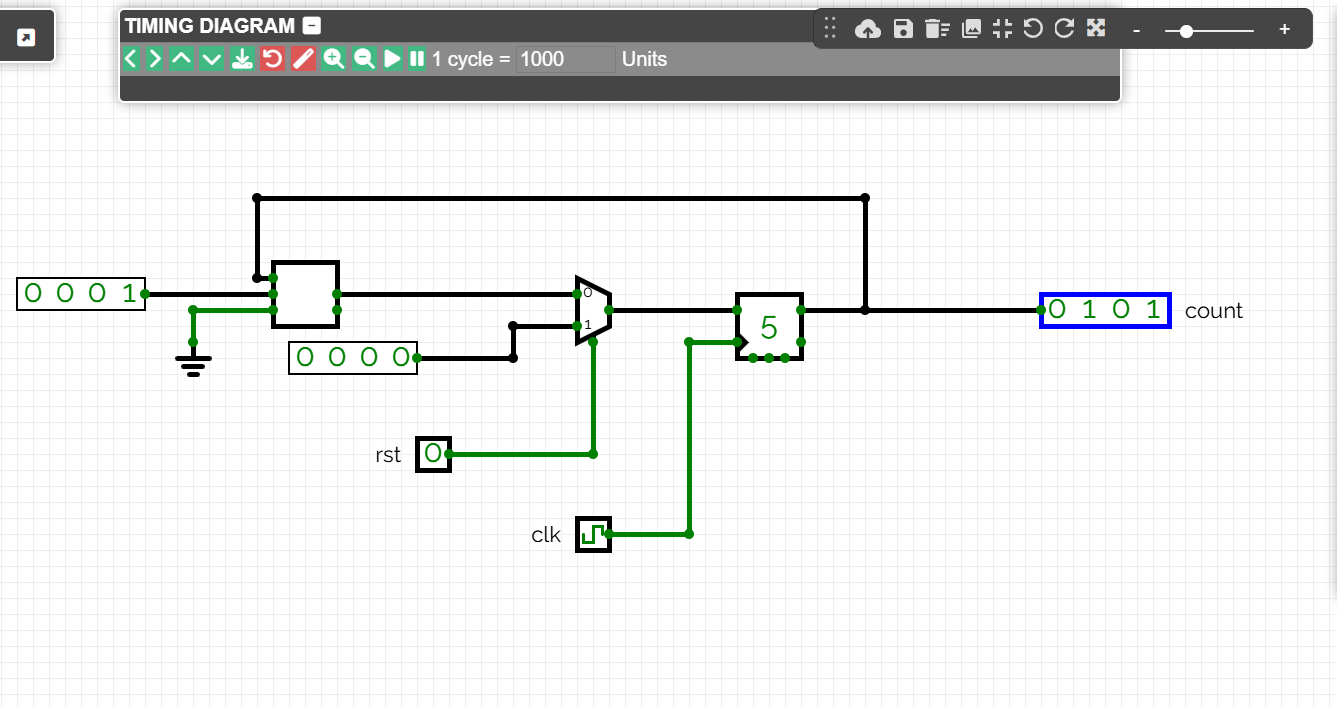

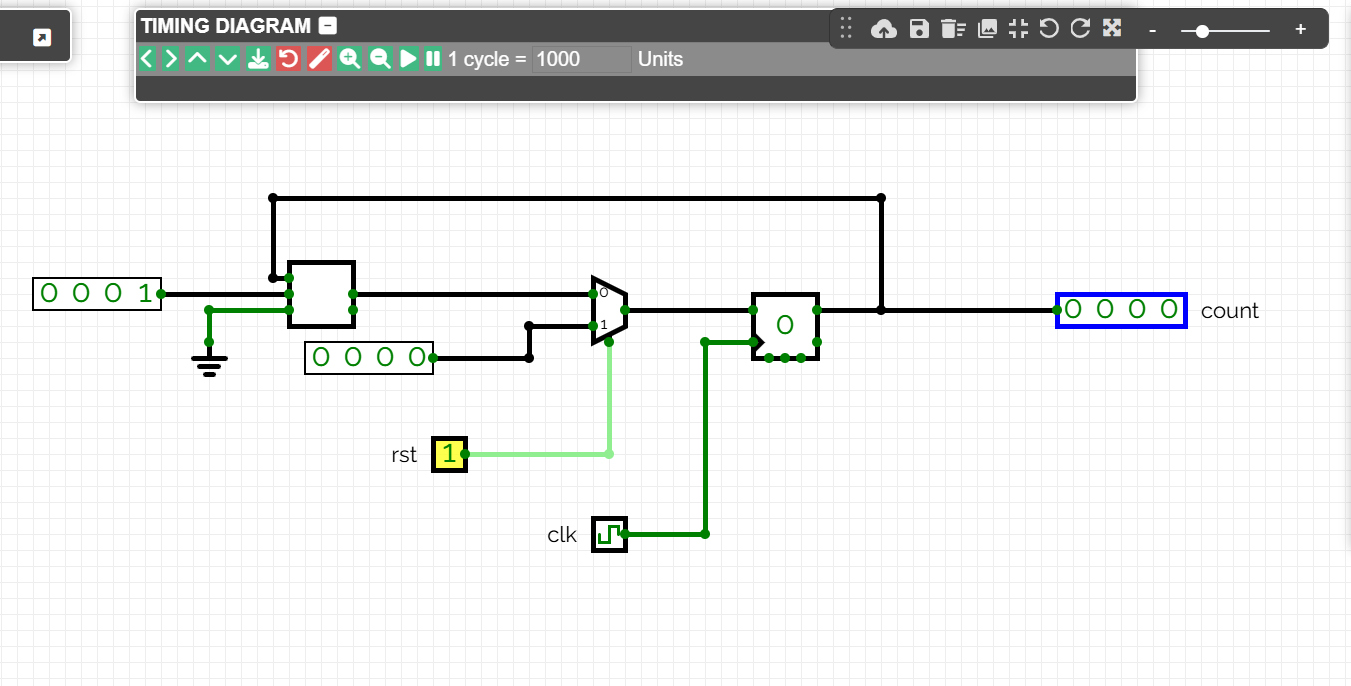

Exemple: Comptador de 4 bits

En aquest exemple veurem com realitzar un comptador de 4 bits.

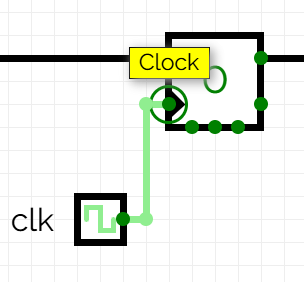

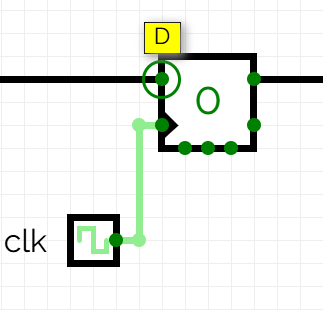

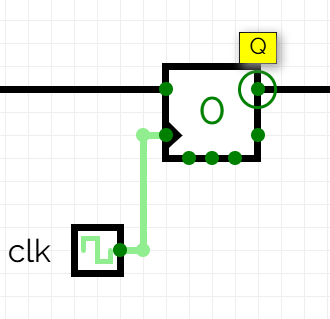

Les connexions del biestable que ens interessen són la D i Q, que marquen l'entrada i sortida de l'element de memòria, i també CLK, que és l’entrada del senyal de rellotge. L'entrada de rellotge representa sovint amb un triangle a l'interior de l'element.

El biestable D també compta amb altres entrades com enables i resets que permeten reiniciar o eliminar estats d’informació. També té una sortida negada

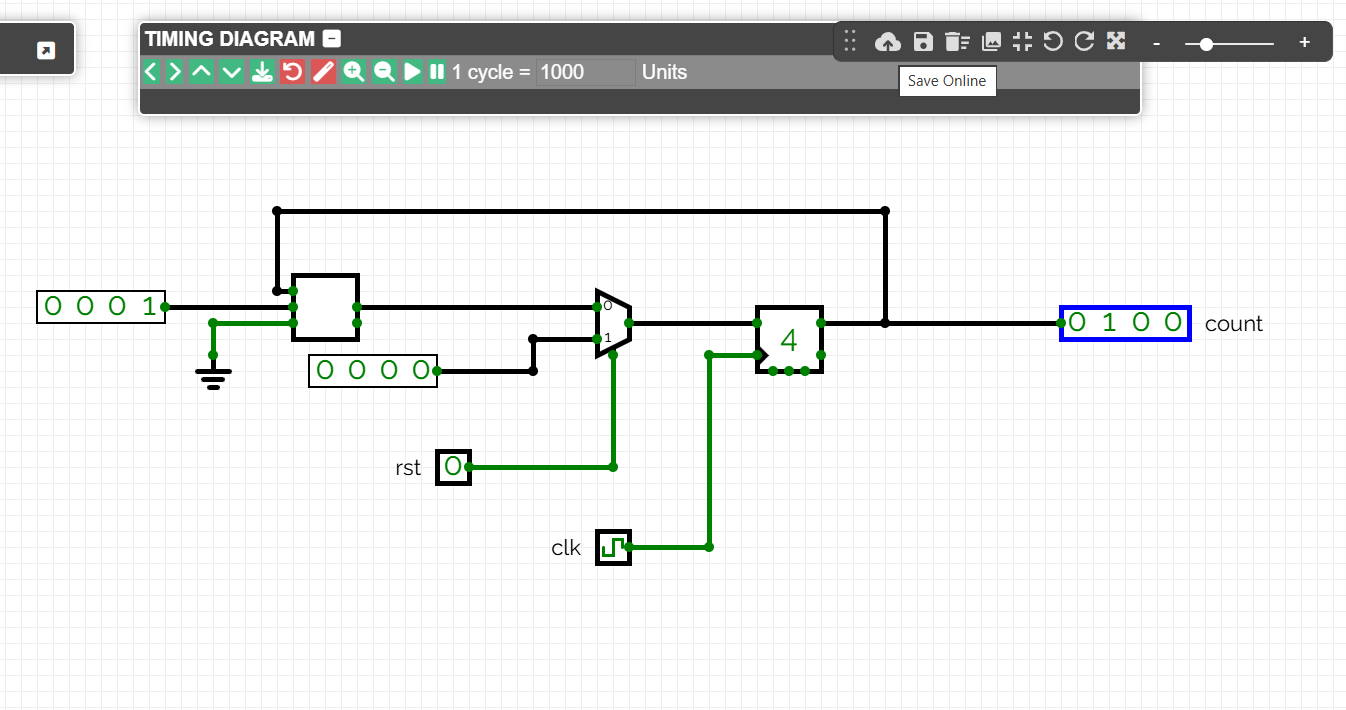

Volem un comptador que segueixi una seqüència binària de 4 bits, de valors successius entre el 0000 i el 1111. També volem incloure un senyal de reset que retorni la sortida a 0000. Aquest comportament es pot aconseguir amb un sumador, un multiplexor i un biestable de 4 bits com a la figura.

El pols de rellotge farà que el sumador afegeixi una constant 0001 al valor de sortida del biestable. En aquest exemple passant d'un valor 0100 a 0101.

El multiplexor forçarà el reinici. Al entrar un senyal rst l'estat del biestable passarà a ser 0000.

CircuitVerse inclou una entrada Asyncronous reset als biestables. Per fer un reinici asíncron cal eliminar el multiplexor i connectar el senyal

Exercicis a Jutge.org: Introduction to Digital Circuit Design

- Toggle

- 2-bit counter

- Mod-3 counter

- 4-bit counter

- Unconventional cyclic counter

- Up-down counter

- Mod-7 up-down counter

Recorda que per accedir als exercicis i perquè el Jutge valori les teves solucions has d'estar inscrit al curs. Trobaràs totes les instruccions aquí.

Xavier Casas, Francesc Madrid

Lliçons.jutge.org

© Universitat Politècnica de Catalunya, 2026